Sistemas Embarcados

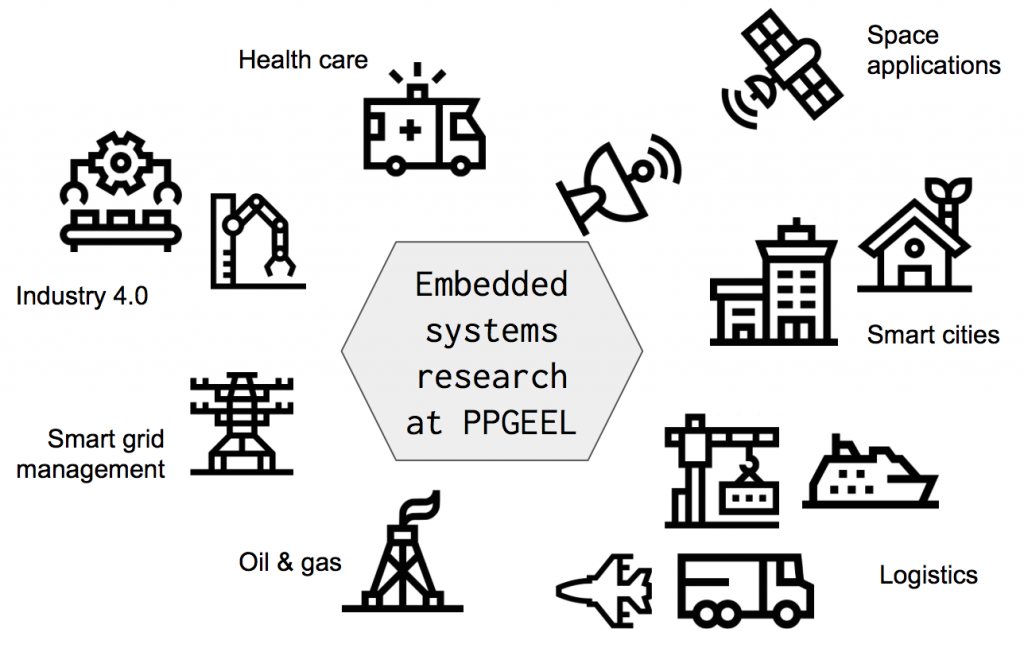

Sistemas embarcados são construídos a partir de uma combinação de componentes de hardware e software, sendo usados como controladores e unidades de processamento em uma variedade de aplicações críticas, resultando em importantes desafios de pesquisa. Exemplos típicos são os sistemas de bordo para satélites ou dispositivos de IoT. Comumente, sistemas embarcados devem cumprir requisitos rigorosos, como baixo consumo de energia, restrições de área, comunicação eficiente, confiabilidade ou segurança crítica. Alguns dos tópicos de pesquisa na subárea de sistemas embarcados do PPGEEL estão listados a seguir.

Tópicos de pesquisa

- Arquitetura de computadores: interface software/hardware

- Criptografia e aritmética computacional em hardware

- Instrumentação, IoT e Indústria 4.0

- Projeto VLSI

- Sistemas aeroespaciais e críticos

- Sistemas biomédicos

- Sistemas operacionais e de tempo real

- Software embarcado

- Tolerância a falhas e confiabilidade

Grupos de pesquisa

Laboratórios

Pesquisadores

Sistemas Embarcados:

- Anderson Wedderhoff Spengler

- Eduardo Augusto Bezerra

- Hector Pettenghi Roldan

- Fabian Leonardo Cabrera Riano

- Fernando Rangel de Sousa

Disciplinas

PPGEEL

EEL 510265 - Programação de Sistemas Embarcados (4 créditos)

EEL 510389 - Sistemas Digitais e Dispositivos Lógicos Reconfiguráveis (4 créditos)

EEL 510390 - Introdução ao Projeto VLSI (4 créditos)

EEL 510457 - Circuitos Aritméticos (4 créditos)

DAS 410051 - Sistemas de Tempo Real I (2 créditos)

DAS 410052 -Sistemas de Tempo Real II (2 créditos)

DAS 410053 - Sistemas Distribuídos I (2 créditos)

DAS 410054 - Sistemas Distribuídos II (2 créditos)

DAS 410056 - Projeto e Desenvolvimento de Sistemas Embarcados (2 créditos)

INE 410107 - Sistemas Embarcados (3 créditos)

INE 410114 - Sistemas Embarcados Distribuídos (3 créditos)

INE410123 - Tópicos Especiais em Computação: Sistemas Ciber-Físicos (4 créditos)

INE 410132 - Arquitetura de Computadores (4 créditos)

INE 410133 - Electronic Design Automation (4 créditos)

Further details

Traditionally, embedded systems are implemented partly in software and partly in hardware, and usually developed by separate teams. In complex projects, integration problems are often experienced since the software and hardware groups work separately. To a certain extent the availability of several functional blocks embedded in the same software-based component (e.g. microcontroller, DSP), and accessed directly by the programming language compiler, has allowed the software designer to avoid learning hardware details. However, lately, a whole hardware based implementation was facilitated as a result of recent advances in the Electronic Design Automation (EDA) field. These advances resulted in more efficient synthesis tools available for hardware description languages (e.g. VHDL, Verilog, C like languages). But writing a code targeting a microprocessor compiler is still much easier than writing a similar code targeting a synthesis tool for a hardware implementation. Despite all the restrictions imposed by the EDA tools, there are significant advantages to start by using a hardware description language as VHDL in new embedded designs. With VHDL, the developer has to use the parallel-programming paradigm from the beginning of the design, making the system closer to real world problems. In addition, a well written VHDL code can be employed in both, a configurable device or in an Application Specific Integrated Circuit (ASIC) device.

The use of Field-Programmable Gate Arrays (FPGAs) to implement reconfigurable computer systems is considered as a complement to the traditional software-based design, and their advantages and associated problems are investigated. From the application developer point of view, one of the main problems is the limitation of the supporting tools available, as they are not able to generate proper netlists from software structures as simple as loops. Despite the supporting tools problem, the numerous benefits provided by reconfigurable computing technology are a strong motivation for the research of strategies, which use this technology to build embedded systems having hardware components closely combined with software modules. Needless to say that a hardware based solution is adequate for just certain categories of problems. Applications requiring complex algorithms and data structures still need to be implemented employing software modules as the main processing components.

In this research area at PPGEEL, the FPGA technology is used also as an alternative to ASIC in order to implement advanced arithmetic architectures using Residual Number Systems (RNS) instead of the classical binary base approach. An important research topic is the development of an RNS framework capable of automatically deriving efficient residual number systems improving the computation of arithmetic, signal processing and cryptographic algorithms. More significantly, this framework will further motivate the use of RNS by having a mechanism that eliminates the complexity of developing computational architectures that explore this numbering system arithmetic. This will also motivate the research community working on RNS to further improve the RNS state of the art. A MATLAB tool has been developed in order to generate RNS arithmetic components. Further challenges include the development of a library of RNS components, and also case studies (e.g. RNS based cryptographic elliptic curves, wavelets, DSP applications, ...).

The hardware/software integration subject is further investigated in the context of modern computer architectures. Technological advances allow embedded systems based devices to becoming more and more autonomous, not only for the on-line data processing in mobile applications, but also in the pre-processing of data to be transmitted to remote systems. In the big data era, on-board pre-processing is a de facto need in any mobile application. The availability of low power high resolution sensors, high data rate instruments, a variety of cameras generating a huge amount of pixels to be compressed, among other data intensive operations, result in the need of multi-processed embedded architectures. However, the reliability and energy requirements in mobile devices are stricter, placing the research on this type of parallel processing architecture at the knowledge frontier. However, when considering embedded soft-cores, FPGAs may not deliver the same performance levels as their counterpart physical microprocessors. But there are studies showing that, on the other hand, FPGAs have better energy consumption levels than CPUs and GPGPUs. In order to improve even more the consumption figures in FPGA based systems, and taking advantage of a soft-processor HDL source code availability, the whole architecture of a multiprocessor system-on-chip (MPSoC) should be made energy aware. For instance, the pipeline of a soft-core processor could be reformulated in order to mitigate unnecessary activities. More advanced architectural structures could be added to improve instruction-level control, reducing activities and clock pulses in the system. In order to avoid code compatibility issues, although not recommended, the compiler itself could be modified to generate code more cache optimized, and with a better register usage, always concerned about this type of battery-driven MPSoC implementation. When choosing between performance improvement or energy efficiency, there is always a compromise. Simulations should be performed for each application to identify what is more energy efficient: employing an MPSoC architecture aiming the pre-processing to minimize the amount of data to be transmitted; or performing a minimal pre-processing, using a more traditional approach, which will result in a large amount of data to be transmitted.

Embedded systems built from a combination of hardware and software components are used as the controllers and processing units of a variety of applications, and the critical ones result in important research challenges. When using a combined software and HDL based implementations targeting embedded critical applications, special attention should be given to system reliability assurance. There are several reliability improvement strategies available in the literature, and the starting point for any strategy is the definition of the fault model to be adopted. The strategies aim to improve dependability figures as reliability, availability, maintainability and safety. In order to improve these figures, Fault Tolerance strategies at the software and hardware levels can be used. The starting point for any fault tolerance strategy is the use of test procedures aiming error detection, which can be followed by error isolation and correction. The fault tolerance is then reached through redundancy techniques.

A typical example of a critical application is the on-board system of a satellite. These embedded systems must comply with very strict requirements. The software and hardware components employed in this sort of system should be able to cope with low power consumption, while providing a considerable throughput. On-board weight and area occupation are also important concerns. However, SRAM based FPGAs are not still used as a primary on-board computer in space applications, as the SRAM technology is radiation susceptible. However, the FPGA's configuration memory is very flexible allowing on-the-fly modifications in on-board functionalities. These reconfigurability feature is an important research topic under investigation in this area at PPGEEL/UFSC.